芯片封装热阻仿真计算案例

2023.05.09

案例提要:

本章以芯片封装为案例,说明如何利用Ansys Icepak计算IC封装的(芯片Die与空气间的热阻)、 (芯片Die与电路板间的热阻)及(芯片Die与封装表面间的热阻)。

针对封装热阻而言,计算放置于JEDEC(美国联合电子设备工程协会)标准机箱内自然对流及强制队留下的热阻数据。部分内容参照了JEDEC测试系列的表准[JESD51]。Ansys Icepak为了仿JEDEC标准测试规范,所有设置皆按JESD51设置标准来设计与进行。

方案重点:

- 通过JEDEC标准仿真出芯片的Rja、Rjb及Rjc。

- 导入芯片封装ECAD → Compact + ECAD (非采用Icepak/JEDEC中Detail模型)

JEDEC是什么?

JEDEC(Joint Electron Device Engineering Council)是一个推动半导体元器件领域标准化的行业组织。半导体制造商以及电力电子领域的从业者不可避免地会涉及到很多行业标准。作为大原则,无论热相关的项目还是其他项目,其测试方法和条件等都要符合行业标准。其原因不言而喻:因为如果方法和条件各不不同,就无法比较和判断好坏。

在JEDEC标准中,与“热”相关的标准主要有两个:

- JESD51系列:包括IC等的封装的“热”相关的大多数标准。

- JESD15系列:对仿真用的热阻模型进行标准化。

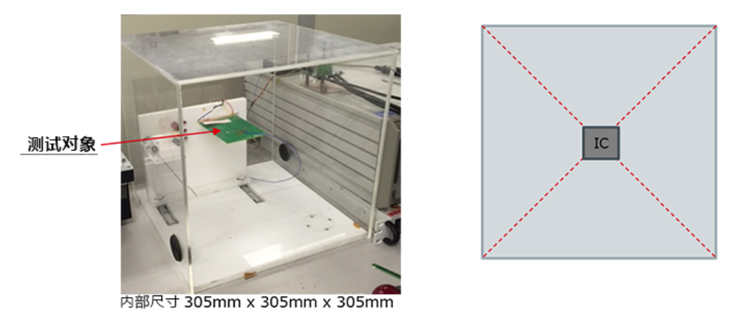

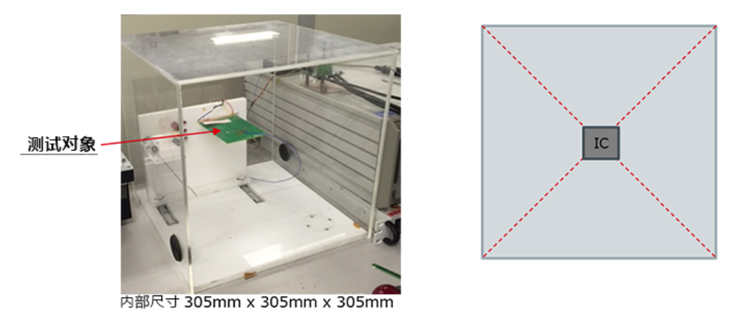

JESD51-2A中规定了热阻测试环境。以下是符合JESD51-2A的热阻测试环境示例。

完整资料请登入会员下载PDF

档案下载:

编号

档名 |

class

版本 |

标题

叙述 |

建立时间

上次更新 |

状态 |

下载 |

23III-T16

2023-05-EBU-(曾家麟) 芯片封装热阻仿真计算案例.pdf |

|

芯片封装热阻仿真计算案例

|

2023-05-09 15:26:09

2023-05-09 16:56:23 |

需登入才能下载 |

下载 |